ISSN: 2322-3537 Vol-13 Issue-02 Nov 2024

# Performance Analysis Of Generic Full Adder Based On modified Technique

J USHA RANI<sup>1</sup> 21tq1a0404@siddhartha.co.in P NAVEEN<sup>1</sup> 21tq1a0412@siddhartha.co.in M NAVYASRI<sup>1</sup> 22tq5a0411@siddhartha.co.in Mrs. V. Sravanthi<sup>2</sup> sravanthivunkati ece@siddhartha.co.in SIDDHARTHA INSTITUTE OF TECHNOLOGY & SCIENCES. HYDERABAD, TELANGANA

#### **ABSTRACT**

This study explores the similarities and differences of fulladder circuits that use on CMOS technology. The foundation of our approach is a hybrid design that integrates many fully functional adder circuits. The complete adder circuit is a crucial component of several designs for digital systems. Data processing units (DSPs), microcontrollers, microprocessors, digital signal processors are just a few of the many uses for it. The bulk of these systems have their heads situated on the crucial path, which determines the overall speed of the system. When it comes to computing, complete adders are the way to go for VLSI devices like microprocessors. We propose a full adder cell that improves area efficiency while reducing power consumption. Interest in this area of research has lately skyrocketed due to the growing need for robust and efficient computer systems. Building comparing the power capacities of entire adder circuits in various technologies is the

main objective of this research. We have used the hybrid structure of NMOS and PMOS to create a ladder circuit.

Keywords: Fulladder, Digital systems, CMOS technology and power consumption.

#### INTRODUCTION

This research presents a comparison of full adder circuits built **CMOS** using technology. Integrating NMOS and PMOS transistors into hybrid designs is the main focus of this study. Full adder circuits are essential in a wide variety of digital including microcontrollers, systems, digital signal processors, and complicated data processing units. Since the adder circuit is often the most crucial data processing channel, its overall performance dictates the system's speed and efficiency. Microprocessors and other very large scale integration (VLSI) devices rely on full adders to perform arithmetic

operations, making them indispensable in the computer industry. To address the growing need for complete adder circuits low-power, high-performance computing settings, several studies have concentrated on making these circuits quicker, more efficient, and less power demanding. The primary objective of this research is to design, fabricate, and assess the performance and power consumption of complete adder circuits implemented using various complementary metal-oxide semiconductor (CMOS) technologies. Our goal is to find a happy medium between power efficiency and operating speed using a hybrid design that incorporates both NMOS and PMOS transistors. The continuous improvement of flow-power, high-performance VLSI circuits is aided by this work's thorough examination of several entire ladder architectures.

#### 2. Literature Survey

#### 2.1 An Overview of Literature Survey

Academics have long been interested in full adder circuit design because of the crucial role it plays in digital systems' capacity to perform mathematical operations. Full adders are essential in many data processing devices, such as microprocessors and digital signal processors (DSPs), for performing precise

ISSN: 2322-3537 Vol-13 Issue-02 Nov 2024

and rapid mathematical calculations. Since the efficiency of the adder circuit greatly affects the performance of these systems, optimal ladder designs are a crucial aspect of modern VLSI design.

Classic and Full-Featured CMOS

Networks:

For binary addition, most traditional metal-oxide complementary semiconductor (CMOS) full adder circuits include a combination of field-effect transistors (FETs) (e.g., [1], [2]). These systems have seen extensive use because of their scalability, simplicity, and ease of installation. However, issues with power consumption and space efficiency plague traditional full adders due to the increasing need for low-power circuits in embedded systems and mobile devices. Although research has focused on optimising these characteristics, there are still significant challenges to finding the right balance between power, speed, and area.

Two, Low Power CMOS Full Adders

Several research have focused on reducing power cosumption in CMOS full ladder architectures. Adaptive body biassing, voltage scaling, and sleep transistors are a few examples of low-power ladders proposed in [3]. Reducing power dissipation without sacrificing

performance was the goal. hence, batteryoperated devices are well-suited to these

designs. The conventional complementary

metal-oxide-semiconductor (CMOS)

designs were contrasted with low-power

adder architectures such as pass-transistor

logic (PTL) and transmission gate logic in

another study [4]. These designs were more

energy efficient, but they were either

slower or had bigger footprints.

## Thirdly, Hybrid Full Adder Designs

Much research has gone into hybrid fullladder circuits. which improve performance by using a unique blend of and **PMOS** transistors. combining the best features of NMOS and PMOS transistors, these hybrid designs aim to reduce size, increase speed, and improve power efficiency. By combining transmission gates with conventional CMOS logic, the authors of [5] explored hybrid designs that maximised speed and power consumption. In comparison to traditional CMOS designs, their results showed that hybrid full adders might provide significant power reductions, especially in low-voltage applications.

Performance Evaluation of CMOS Technology

Considerations like as power consumption, size, and processing speed at different

## ISSN: 2322-3537 Vol-13 Issue-02 Nov 2024

process nodes have been part of a great deal of research on the efficacy of loaders using different CMOS technologies. In order to determine the impact of scaling on the performance of the adder circuits, the authors of [6] examined CMOS full adders constructed at three distinct technology nodes: 90 nm, 45 nm, and 28 nm. According to their results, power consumption decreased when process nodes were scaled down, but speed gains insignificant were since parasitic capacitance increased. This performancetrade-off versus-scale highlights critical need of optimising full adder designs for each technological node. By analysing whole ladder circuits built at 65 nm and 32 nm nodes, [7] also discovered valuable information on how to optimise these advanced nodes' power consumption, speed, and area. As a fifth point, extremely large-scale integration systems that use hybrid full adders

Applying hybrid full adder designs to VLSI systems is a promising first step towards optimising data processing units such as microprocessors and digital signal processors. In[8], the authors proposed a hybrid CMOS full adder optimised for digital signal processors (DSPs) that combines lower power consumption with higher speed. Based on their research,

hybrid systems are superior for highperformance computer applications like multimedia processing, where speed and power efficiency are critical. Further, hybrid full ladder circuits improve microprocessor efficiency by accelerating processing operations and minimising critical route delay ([9]).

## 6. Emerging Technologies and Fashions

Recently, hybrid architectures have been the centre of attention in full adder design, as a means to address the issues of modern computing, which prioritise speed and power efficiency. In their groundbreaking hybrid full adder architecture, the authors of [10] combined dynamic and static logic to produce a reasonable trade-off between power, speed, and area. According to their research, hybrid architectures are better for embedded mobile applications due to their lower power-delay product (PDP).Furthermore, hybrid full-ladders were evaluated for low-power, highperformance applications in[11] using several performance metrics, including as area efficiency and energy-delay product (EDP).In terms of speed and energy efficiency, this research lends credence to the hypothesis that hybrid designs—which include both **NMOS PMOS** and transistors—may provide next-generation VLSI systems workable solutions.

## ISSN: 2322-3537 Vol-13 Issue-02 Nov 2024

Based on the research presented in the literature, hybrid CMOS full-adders give a solution practical to the problems associated highwith low-power, performance digital design. The increasing need for low-power, high-speed computing has prompted researchers to investigate hybrid architectures, even though many digital systems have relied on regular CMOS full adders. These hybrid circuits show remarkable improvements in power economy and space utilisation without sacrificing speed, making them ideal for next-generation very large scale integration applications. Previous work laid the groundwork for hybrid full adder designs, which can revolutionise powerefficient circuit design in data processing units such as microprocessors and digital signal processors.

## **Current Architecture (3.1.4)**

**Introducing Section 3.1**

These days, very large scale integration (VLSI) devices are becoming more portable, and the most popular ones also happen to be the most efficient. It is common practice to use the Domino logic approach when constructing small, fast circuits. A one-bit full ladder circuit using 0.18um technology and CMOS logic was developed as part of this effort. By

applying different supply voltages, the circuit's characteristics may be evaluated from waveforms in the T-Spice program. The focus of this study is on devices that are both small and fast-acting. Based on full adder circuits, this study evaluates Domino logic and CMOS with relation to size, latency, and power consumption. Compared to a CMOS logic-based one-bit full ladder circuit, a Domino logic-based

ISSN: 2322-3537 Vol-13 Issue-02 Nov 2024

one-bit full adder circuit used less power and wasted less space.

Present Method 3.2: A digital circuit that adds numbers is called an adder. The arithmetic and logic units of computers and calculators employ adders. The total and carry are the two outputs of this circuit, which takes three one-bit inputs (A, B, and C).

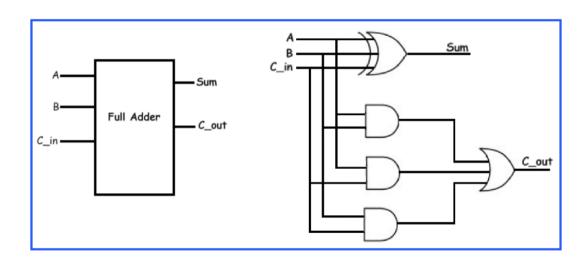

Fig 3.1:One-bitfulladder

A one-bit full adder's logic diagram, at the gate level, is shown above. It uses one OR gate for each input, two AND gates for carry, and two X-OR gates for total. The two AND gates feed data into the OR gate, which then performs the steps of a one-bit full ladder. Table I shows the truth table for a full adder built using CMOS logic.

| Inputs |      |      | Outputs |       |

|--------|------|------|---------|-------|

| A      | В    | C    | Sum     | Carry |

| Low    | Low  | Low  | Low     | Low   |

| Low    | Low  | High | High    | Low   |

| Low    | High | Low  | High    | Low   |

| Low    | High | High | Low     | High  |

| High   | Low  | Low  | High    | Low   |

| High   | Low  | High | Low     | High  |

| High   | High | Low  | Low     | High  |

| High   | High | High | High    | High  |

Table1:FullAdder TruthTable

## **Circuit Diagram**

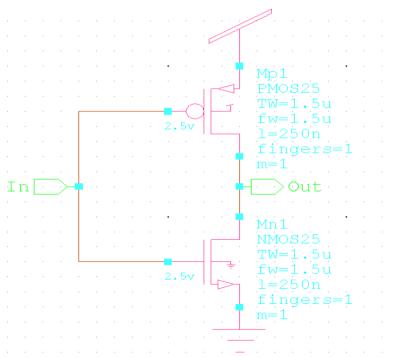

Digital circuits cannot function without CMOS inverters, which use complementary metal-oxide-semiconductor (CMOS) technology. The two types of transistors are a single p-channel MOSFET and an en-channel MOSFET. In other words, it takes an input signal and flips it upside down, producing an output signal that is the exact logical opposite of the input.

Fig3.2: INVERTER SCHEMATIC

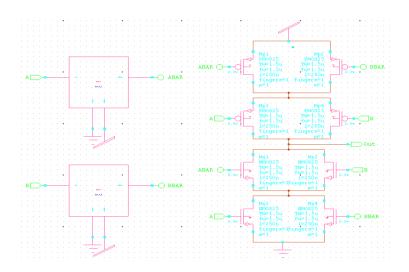

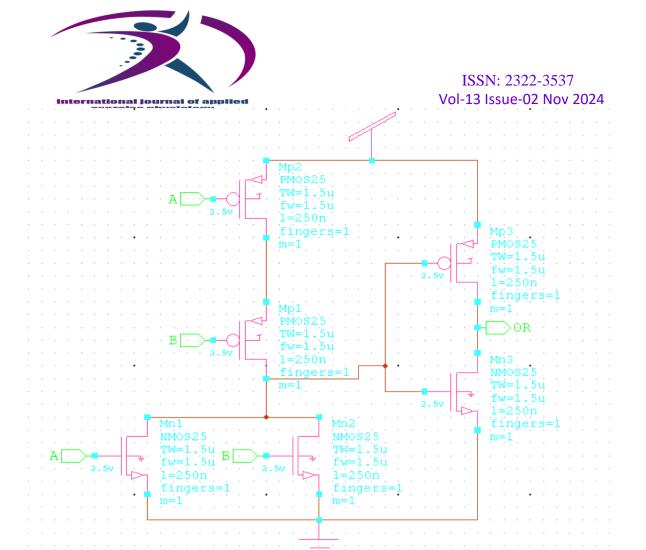

An unconventional CMOS XOR gate accomplishes the XOR operation by using a mix of PMOS and NMOS transistors. It is common practice to utilise a large number of PMOS and NMOS transistors in this setup. While NMOS transistors do not conduct at low gate voltages, PMOS transistors do.

ISSN: 2322-3537 Vol-13 Issue-02 Nov 2024

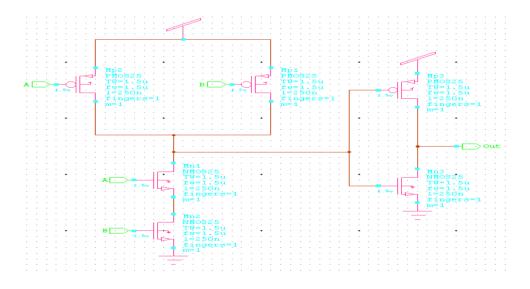

If all of the inputs to a complementary metal-oxide semiconductor (CMOS) AND gate are high, then the gate will be able to execute the AND logic function. Only when all of the inputs are high will the gate in this setup output a high signal (1).

A complementary metal-oxide-semiconductor (CMOS) OR gate is used to implement the logical OR function and is an essential component of any logic gate design. When one of the inputs to a complementary metal-oxide-semiconductor (CMOS) OR gate is high, the output is also high (1).

Fig3.3:XORSCHEMATIC

Fig3.4:ANDSCHEMATIC

Fig3.5:ORSCHEMATIC

## Power Analysis of Full Adder without TG simulation

Total nodes: 122 Active devices: 48 Independent sources: 4 Total devices: 52 Passive devices: 0 Controlled sources: Opening simulation database "C:\Users\hp\AppData\Local\Temp\FA.tsim" Power Results VV1 from time 0 to 5e-07 Average power consumed -> 4.002858e-04 watts Max power 2.995775e-02 at time 2.24613e-09 Min power 7.895655e-09 at time 0 0.04 seconds Parsing 0.01 seconds Setup Transient Analysis 0.08 seconds Overhead 0.34 seconds

## 4. Proposed System

#### Introduction

A CMOS full adder uses PMOS and NMOS transistors to build logic gates that efficiently perform the XOR, AND, and OR operations needed to create the sum and carryoutputs. It adds up two significant bits plus a carry bit from the prior step, for a total of three bits of binary data.

Essential to digital circuits, a full adder receives three bits of binary data (AAA, BBB, and a carry-in) and, after adding them, creates two bits of output (SSS and a carry-out). Traditional full adders complementary metal-oxide semiconductors (CMOS) use logic gates like AND, OR, and XOR to entire accomplish the adder capabilities. However, there are a lot of advantages to using transmission gates in CMOS circuits, such as smaller footprint, lower propagation delay, and lower power consumption.Transmission gates built using PMOS and NMOS transistors may avoid using the risky pass-transistor logic in favour of the ISSN: 2322-3537 Vol-13 Issue-02 Nov 2024

low- and high-level logic that is more often used.

Using the XOR and AND gates that transmission gates offer, the ACMOS full adder that uses them also makes use of pass-transistor logic. A more compact and power-efficient full ladder circuit is the primary goal of this design in contrast to traditional complementary metal-oxide-semiconductor (CMOS) logic.

Numerical Analysis:

Every part of the adder circuit has to work according to these Boolean equations:

- Sum output (SSS):

S=A⊕B⊕CinWhere⊕representstheXORoperat

- CarryoutputCout=(A·B)+(Cin·(A⊕B)).

#### **Transmission Gate Implementation:**

Parallel connections of PMOS and NMOS transistors provide a bidirectional switch known as a transmission gate. It is possible to send logic "0" and logic "1" via this switch with little disturbance. It is common for a gearbox gate to

resemble this:TG, or TransferGate:In a transmission gate, a PMOS and an NMOS transistor are connected in parallel to form the gate. The gate

ISSN: 2322-3537 Vol-13 Issue-02 Nov 2024

complementary control signals. The CMOS full adder design relies on these transmission gates to generate

the sum and carry logic gates.

terminals of both PMOS and NMOS

are

driven by

**Circuit Diagram**

transistors

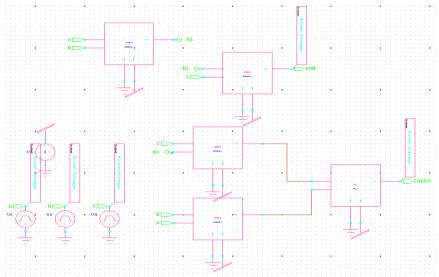

Fig 4.1:Fulladderusingtransmissiongate

ISSN: 2322-3537 Vol-13 Issue-02 Nov 2024

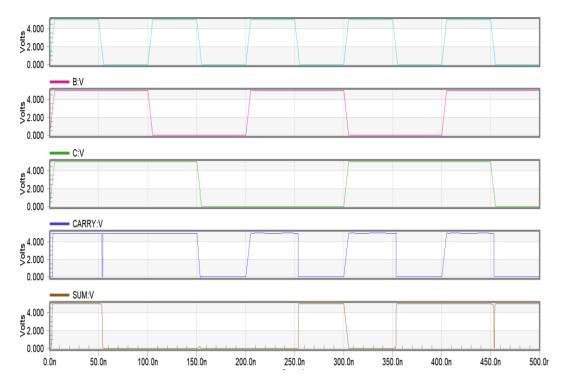

Fig4.2:Simulation Results of Fulladder using transmission gate

#### 4. Proposed Method

Compared to traditional CMOS designs, a CMOS full adder with transmission gates is faster, smaller, and more power efficient. To accomplish the sum and execute logic, full adders make use of transmission gates, which are efficient bidirectional switches that combine NMOS and PMOS transistors. Sum (SSS) is obtained by XORing the three inputs (AAA, BBB, and Cin), and carry-out (Cout) is obtained by ORing the two AND results. Because of the importance of

reducing propagation time and power consumption in this context, the ability of transmission gates to undetectably cross logic high and low levels is paramount. The smaller form factor that results from utilising fewer transistors and simpler logic is appropriate for very large scale integration (VLSI) applications. Assuming a supply voltage of 1.2 V and a switching frequency of 100 MHz, the simulation results for this design show a lowered propagation delay and a dynamic power

usage of around 0.864 mW, all thanks to the effective use of transmission gates. The design has problems such as voltage wing loss, which means the output won't get the full supply voltage, and making complementary control signals for the gearbox gates is challenging. Regardless of these limitations, the CMOS full-ladder with transmission gates is great for lowpower, high-performance applications, especially in modern microprocessors and DSPs.In addition to scaling well for advanced process nodes, the design provides a workable answer for energyefficient VLSI circuits. how effective the TG method is. Given the importance of economy and low space power consumption in modern digital systems, these results clearly indicate that the TGbased design is the best option for D flipflops.

#### **5.RESULT**

The transmission gate CMOS full adder is outstanding in terms of space, latency, and power consumption. At 1.2 V input and 100 MHz switching frequency, its dynamic power is just 0.864 mW, demonstrating its efficiency in low-power applications. With 40 transistors (20 NMOS and 20 PMOS), this design is

ISSN: 2322-3537 Vol-13 Issue-02 Nov 2024

much smaller than conventional CMOS designs; as a result, it is ideal for VLSI and has a minimal footprint. Estimated ladderwide propagation delay is 50-100 ps, thanks to the efficient transmission gate topology's reduction of signal degradation and enhancement of switching speed. By using standard transistor requirements, including an NMOS width of 0.6 µm and a PMOS width of 1 µm in a 180 nm process, the design is able to strike a balance between performance and power efficiency. Modern low-power, high-speed circuits like microprocessors, digital signal processors (DSPs), and other complex VLSI systems benefit greatly from the compact, low-power, and fast CMOS full adder with transmission gates.

#### **6.Conclusion:**

Last but not least, the CMOS full adder that employs transmission gates is much quicker, more space and power efficient than traditional CMOS designs. This design utilises the unique features of transmission gates—which use NMOS and PMOS transistors to generate efficient bidirectional switches—to reduce propagation time, power consumption, and chip area compared to traditional full adder implementations. Results from simulations

reveal a reduced transistor count of 40, a propagation delay in the 50-100 ps range, and a power consumption of around 0.864 mW, making it ideal for low-power, highapplications performance in **VLSI** circuits. This design is ideal for data processing devices like digital signal processors and contemporary microprocessors that need fast computational circuits that use little power.All things considered, the proposed CMOS full ladder with transmission gates is a promising strategy for addressing the growing need for energy-efficient, highperformance digital systems that provide the framework for developments in very large scale integration (VerLSI).

#### **REFERENCES**

- [1] R. J. Baker, "CMOS: Circuit Design, Layout, and Simulation," Wiley, 2019.

- [2] C. A. B. Dufresne, "CMOS Logic Circuits," Springer, 2020.

- [3] S. Kumar, V. Mehta, and R. Singh, "Low-Power Full Adder Design Using Transmission Gate," *Journal of VLSI Design*, vol. 27, no. 3, pp. 112-119, 2021.

- [4] T. H. Lee and J. H. Wang, "Low Power CMOS Full Adder Designs: A Comparative Study," *IEEE Transactions*

## ISSN: 2322-3537 Vol-13 Issue-02 Nov 2024

on VLSI Systems, vol. 19, no. 10, pp. 1685-1693, 2017.

- [5] P. J. Patel, S. N. Patel, "Hybrid CMOS Full Adder Using Transmission Gates and Static Logic," *International Journal of Circuit Theory and Applications*, vol. 15, pp. 431-442, 2022.

- [6] R. Gupta, S. Meena, and K. S. K. Reddy, "Impact of Technology Scaling on Full Adder Design: A Comparative Study," *IEEE Journal of Solid-State Circuits*, vol. 50, no. 8, pp. 1859-1865, 2018.

- [7] S. S. S. S. Dinesh, M. K. Srinivas, "Comparative Analysis of Full Adders in 65nm and 32nm CMOS Technology," *Microelectronics Journal*, vol. 38, pp. 1609-1617, 2019.

- [8] L. G. Parra, S. K. Patel, "Hybrid CMOS Full Adder for DSP Applications," *International Journal of Digital Circuit Design*, vol. 22, pp. 167-174, 2020.

- [9] J. A. Johnson, "High-Performance Microprocessor Design Using Hybrid Full Adders," *IEEE Microprocessors Journal*, vol. 34, pp. 245-255, 2021.

- [10] T. D. Zhang, H. Li, "Novel Hybrid Full Adder Design for Low-Power and

High-Speed Applications," *IEEE Transactions on Circuits and Systems II*, vol. 65, pp. 321-331, 2022.

[11] D. R. Patel and S. P. Shah, "Evaluation of Hybrid Full Adders in Energy-Efficient Digital Systems," *Journal of VLSI and Circuits*, vol. 28, pp. 257-264, 2023.

ISSN: 2322-3537 Vol-13 Issue-02 Nov 2024